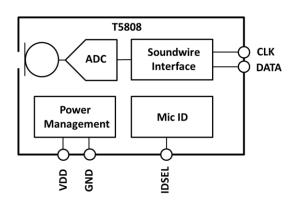

#### **GENERAL DESCRIPTION**

The T5808 is a multi-mode, low noise digital MEMS microphone in a small package. The T5808 consists of a MEMS microphone element and an impedance converter amplifier followed by a fourth-order  $\Sigma$ - $\Delta$  modulator. The digital interface is a MIPI Alliance SoundWire<sup>®</sup> compliant interface which allows bi-directional data flow.

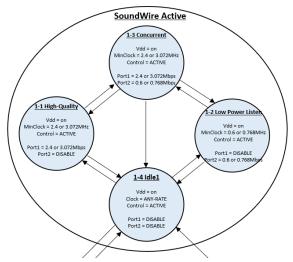

The T5808 has multiple modes of operation: High Quality, Low Power Listen (Always-On), Concurrent and Idle (sleep). The T5808 has high SNR and high AOP in all operational modes.

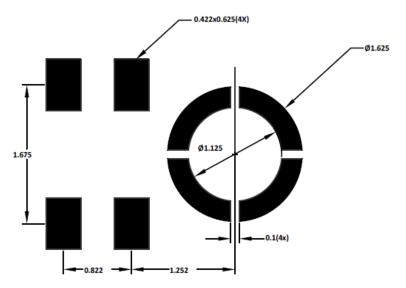

The T5808 is available in a standard  $3.5 \times 2.65 \times 0.98$  mm surface-mount package. It is reflow solder compatible with no sensitivity degradation.

#### **APPLICATIONS**

- Smartphones

- Microphone Arrays

- Smart Speakers

- Headsets

- Tablets and Notebook PCs

#### **FEATURES**

| SPEC                    | HIGH QUALITY MODE                   | LOW POWER LISTEN                    |  |  |  |

|-------------------------|-------------------------------------|-------------------------------------|--|--|--|

|                         |                                     | MODE                                |  |  |  |

| Sensitivity             | -41 dB FS ±1 dB                     | -26 dB FS ±1 dB                     |  |  |  |

| SNR                     | 66 dBA                              | 62 dBA                              |  |  |  |

| Current                 | 650 μA                              | 215 μΑ                              |  |  |  |

| AOP                     | 135 dB SPL                          | 120 dB SPL                          |  |  |  |

| Microphone Data<br>Rate | 2.4 Mbps or 3.072 Mbps <sup>1</sup> | 0.6 Mbps or 0.768 Mbps <sup>1</sup> |  |  |  |

| SoundWire Bus           | Integer Multiple of Microphe        | one data rate up to 9.6 MHz or      |  |  |  |

| Clock Frequency         | 12.288 MHz                          |                                     |  |  |  |

T5808

Note 1: Acoustic performance for 2.4MHz, 0.768MHz

- 3.5 × 2.65 × 0.98 mm surface-mount package

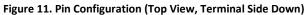

- Extended frequency response from 40 Hz to 20 kHz

- Low power: 215 μA in Low Power Listen Mode

- Sleep (ClockStop) Mode: 9 μA

- MIPI Alliance SoundWire Slave v1.1 compliant

- IDSEL pin for multi-microphone enumeration (up to 7 devices)

- Compatible with Sn/Pb and Pb-free solder processes

- RoHS/WEEE compliant

#### FUNCTIONAL BLOCK DIAGRAM

#### **ORDERING INFORMATION**

| PART             | TEMP RANGE     | PACKAGING         |

|------------------|----------------|-------------------|

| MMICT5808-00-012 | –40°C to +85°C | 13" Tape and Reel |

# **⊗TDK**

# TABLE OF CONTENTS

| 1 |

|---|

| 1 |

| 1 |

| 1 |

| 1 |

| 2 |

| 4 |

| 4 |

| 4 |

| 4 |

| 5 |

| 5 |

| 5 |

| 6 |

| 6 |

| 6 |

| 7 |

| 7 |

| 9 |

| 9 |

| 1 |

| 1 |

| 2 |

| 2 |

| 2 |

| 3 |

| 3 |

| 3 |

| 4 |

| 5 |

| 6 |

| 6 |

| 6 |

| 7 |

| 9 |

| 9 |

| 5 |

| 8 |

|   |

# **⊗TDK**

# **T5808**

| Absolute Maximum Ratings                     |    |

|----------------------------------------------|----|

| Table 21. Absolute Maximum Ratings           |    |

| ESD Caution                                  |    |

| Soldering Profile                            |    |

| Table 22. Recommended Soldering Profile*     |    |

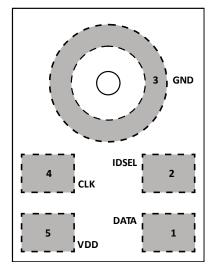

| Pin Configurations And Function Descriptions |    |

| Table 23. Pin Function Descriptions          |    |

| Typical Performance Characteristics          |    |

| Supporting Documents                         |    |

| Application Notes – General                  |    |

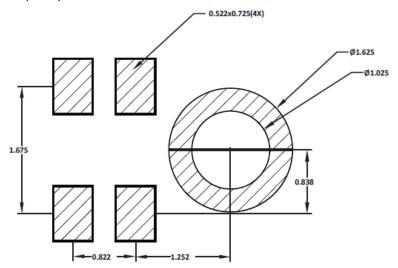

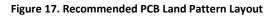

| PCB Design And Land Pattern Layout           |    |

| PCB Material And Thickness                   |    |

| Handling Instructions                        |    |

| Pick And Place Equipment                     |    |

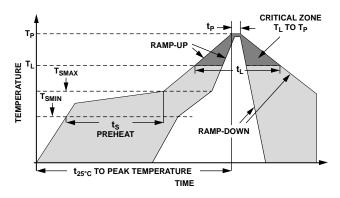

| Reflow Solder                                |    |

| Board Wash                                   |    |

| Outline Dimensions                           |    |

| Ordering Guide                               |    |

| Revision History                             | 40 |

|                                              |    |

#### TABLE 1. ACOUSTICAL/ELECTRICAL CHARACTERISTICS – GENERAL

$T_A = 25^{\circ}C$ ,  $C_{LOAD} = 60 \text{ pF}$  unless otherwise noted. Typical specifications are not guaranteed.

| PARAMETER                         | CONDITIONS                              | MIN  | ТҮР          | MAX  | UNITS | NOTES |

|-----------------------------------|-----------------------------------------|------|--------------|------|-------|-------|

| PERFORMANCE                       |                                         |      |              |      |       |       |

| Directionality                    |                                         | Omni |              |      |       |       |

| Output Polarity                   | Input acoustic pressure vs. output data |      | Non-Inverted |      |       |       |

| Supply Voltage (V <sub>DD</sub> ) |                                         | 1.62 | 1.8          | 1.98 | V     |       |

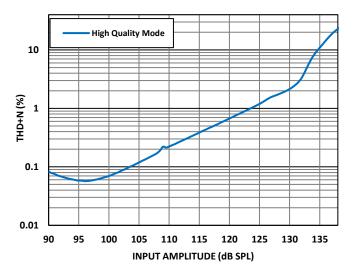

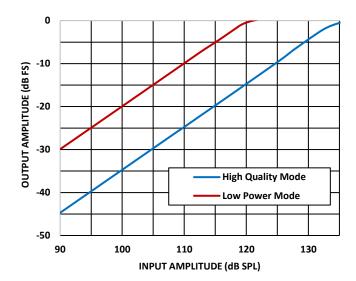

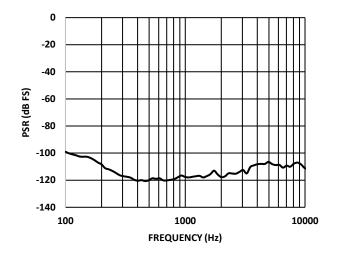

#### TABLE 2. ACOUSTICAL/ELECTRICAL CHARACTERISTICS - MODE 1-1 (HIGH QUALITY MODE)

$T_A = 25^{\circ}$ C, VDD = 1.8 V,  $f_{swclk} >= 2.4$  MHz (Note 2), Mic Data Rate = 2.4 Mbps or 3.072 Mbps,  $C_{LOAD} = 60$  pF unless otherwise noted. Typical specifications are not guaranteed.

| PARAMETER                         | CONDITIONS                                                       | MIN | ТҮР  | MAX | UNITS   | NOTES |

|-----------------------------------|------------------------------------------------------------------|-----|------|-----|---------|-------|

| Sensitivity                       | 1 kHz, 94 dB SPL                                                 | -42 | -41  | -40 | dB FS   | 2     |

| Signal-to-Noise Ratio (SNR)       | 20 kHz bandwidth, A-weighted                                     |     | 66   |     | dBA     |       |

| Equivalent Input Noise (EIN)      | 20 kHz bandwidth, A-weighted                                     |     | 28   |     | dBA SPL |       |

| Dynamic Range                     | Derived from EIN and acoustic overload point                     |     | 107  |     | dB      |       |

| Total Harmonic Distortion (THD)   | 94 dB SPL                                                        |     | 0.1  |     | %       |       |

| Power Supply Rejection (PSR) Sine | 1 kHz Sine Wave                                                  |     | -117 |     | dB FS   |       |

| Power Supply Rejection (PSR)      | 217 Hz, 100 mV p-p square wave                                   |     | 114  |     | dB FS   |       |

| Square                            | superimposed on VDD = 1.8 V, A-weighted                          |     | -114 |     | (A)     |       |

| Acoustic Overload Point           | 10% THD                                                          |     | 135  |     | dB SPL  |       |

| Supply Current (Idd)              | $V_{DD}$ = 1.8 V, $f_{swclk}$ = 2.4 MHz, No load                 |     | 650  |     | μΑ      | 3     |

| Supply Current (Idd)              | V <sub>DD</sub> = 1.8 V, f <sub>swclk</sub> = 2.4 MHz, 5 pF load |     | 671  |     | μA      | 3     |

| Supported Ports                   |                                                                  |     |      |     |         |       |

| Data Port 1 (High Quality Mode)   | Active                                                           |     |      |     |         |       |

| Data Port 2 (Low Power-Listen     | Disabled                                                         |     |      |     |         |       |

| Mode)                             | Disabled                                                         |     |      |     |         |       |

| Control Port                      | Active                                                           |     |      |     |         |       |

**Note 2:** Sensitivity is relative to the RMS level of a sine wave with positive amplitude equal to 100% 1s density and negative amplitude equal to 0% 1s density. **Note 3:** f<sub>swclk</sub> should be an integer multiple of the desired Mic Data Rate see table 14 with permissible f<sub>swclk</sub> and Mic Data Rates.

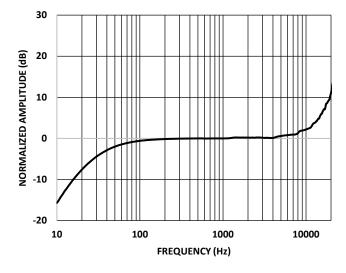

#### TABLE 3. ACOUSTICAL/ELECTRICAL CHARACTERISTICS - MODE 1-2 (LOW POWER LISTEN MODE)

$T_A = 25^{\circ}$ C, VDD = 1.8V,  $f_{swclk} >= 0.6$ MHz (Note 2), Mic Data Rate =0.6 Mbps or 0.768 Mbps  $C_{LOAD} = 60$  pF unless otherwise noted. Typical specifications are not guaranteed.

| PARAMETER                       | CONDITIONS                                                      | MIN | ТҮР | MAX | UNITS   | NOTES |  |

|---------------------------------|-----------------------------------------------------------------|-----|-----|-----|---------|-------|--|

| Sensitivity                     | 1 kHz, 94 dB SPL                                                | -27 | -26 | -25 | dB FS   | 2     |  |

| Signal-to-Noise Ratio (SNR)     | 8 kHz bandwidth, A-weighted, f <sub>swclk</sub> = 0.768MHz      |     | 62  |     | dBA     | 3     |  |

| Equivalent Input Noise (EIN)    | 8 kHz bandwidth, A-weighted, f <sub>swclk</sub> = 0.768MHz      |     | 32  |     | dBA SPL |       |  |

| Signal-to-Noise Ratio (SNR)     | 8 kHz bandwidth, A-weighted, f <sub>swclk</sub> = 0.600MHz      |     | 60  |     | dBA     | 3     |  |

| Equivalent Input Noise (EIN)    | 8 kHz bandwidth, A-weighted, f <sub>swclk</sub> = 0.600MHz      |     | 34  |     | dBA SPL |       |  |

| Dunamia Banga                   | Derived from EIN and acoustic overload point,                   |     | 88  | 00  | dB      | ٩D    |  |

| Dynamic Range                   | f <sub>swclk</sub> = 0.768MHz                                   |     | 00  | -25 | ив      |       |  |

| Total Harmonic Distortion (THD) | 94 dB SPL                                                       |     | 0.1 |     | %       |       |  |

| Acoustic Overload Point         | 10% THD                                                         |     | 120 |     | dB SPL  |       |  |

| Supply Current (L.)             | V <sub>DD</sub> = 1.8 V, f <sub>swclk</sub> = 0.6 MHz , no load |     | 215 |     | μΑ      | 3     |  |

| Supply Current (Idd)            | $V_{DD}$ = 1.8 V, $f_{swclk}$ = 0.6 MHz , 5 pF load             |     | 220 |     | μΑ      | 3     |  |

| Supported Ports                 |                                                                 |     |     |     |         |       |  |

| Data Port 1 (High Quality Mode) | Disabled                                                        |     |     |     |         |       |  |

| Data Port 2 (Low Power-Listen   | Active                                                          |     |     |     |         |       |  |

| Mode)                           | Active                                                          |     |     |     |         |       |  |

| Control Port                    | Active                                                          |     |     |     |         |       |  |

**Note 2**: Sensitivity is relative to the RMS level of a sine wave with positive amplitude equal to 100% 1s density and negative amplitude equal to 0% 1s density. **Note 3**: f<sub>swclk</sub> should be an integer multiple of the desired Mic Data Rate see table 14 with permissible f<sub>swclk</sub> and Mic Data Rates.

# **☆TDK**

#### TABLE 4. ACOUSTICAL/ELECTRICAL CHARACTERISTICS – MODE 1-3 (CONCURRENT MODE)

$T_A = 25^{\circ}$ C, VDD = 1.8 V,  $C_{LOAD} = 60$  pF unless otherwise noted. Typical specifications are not guaranteed.

| PARAMETER                                | CONDITIONS                                         | MIN | ТҮР | MAX | UNITS | NOTES |

|------------------------------------------|----------------------------------------------------|-----|-----|-----|-------|-------|

| Supply Current (Idd)                     | $V_{DD}$ = 1.8 V, $f_{swclk}$ = 2.4MHz , no load   |     | 775 |     | μΑ    | 3     |

| Supply Current (Idd)                     | $V_{DD}$ = 1.8 V, $f_{swclk}$ = 2.4MHz , 5 pF load |     | 796 |     | μΑ    | 3     |

| Acoustical/Electrical Specifications     |                                                    |     |     |     |       |       |

| See Mode 1-1 Specifications for Port 1   | Data                                               |     |     |     |       |       |

| See Mode 1-2 Specifications for Port 2 I | Data                                               |     |     |     |       |       |

| Supported Data Rates                     |                                                    |     |     |     |       |       |

| Data Port 1 (High Quality Mode)          | Active                                             |     |     |     |       |       |

| Data Port 2 (Low Power-Listen Mode)      | Active                                             |     |     |     |       |       |

| Control Port                             | Active                                             |     |     |     |       |       |

Note 3: fswclk should be an integer multiple of the desired Mic Data Rate see table 14 with permissible fswclk and Mic Data Rates.

#### TABLE 5. ACOUSTICAL/ELECTRICAL CHARACTERISTICS – MODE 1-4 (IDLE 1, CONTROL ONLY)

$T_A = 25^{\circ}C$ , VDD = 1.8 V,  $C_{LOAD} = 60 \text{ pF}$  unless otherwise noted. Typical specifications are not guaranteed.

| PARAMETER                           | CONDITIONS                       | MIN | ТҮР | MAX | UNITS | NOTES |

|-------------------------------------|----------------------------------|-----|-----|-----|-------|-------|

| Supply Current (I <sub>dd</sub> )   | V <sub>DD</sub> = 1.8 V, No load |     | 31  |     | μΑ    |       |

|                                     | f <sub>swclk</sub> = 0.6 MHz     |     | 31  |     |       |       |

| Supported Data Rates                |                                  |     |     |     |       |       |

| Data Port 1 (High Quality Mode)     | Disabled                         |     |     |     |       |       |

| Data Port 2 (Low Power-Listen Mode) | Disabled                         |     |     |     |       |       |

| Control Port                        | Active                           |     |     |     |       |       |

#### TABLE 6. ACOUSTICAL/ELECTRICAL CHARACTERISTICS - MODE 2-2 (CLOCK STOP)

T<sub>A</sub> = 25°C, VDD = 1.8 V, C<sub>LOAD</sub> = 60 pF unless otherwise noted. Typical specifications are not guaranteed.

| PARAMETER                            | CONDITIONS                                                   | MIN | ТҮР | MAX | UNITS | NOTES |

|--------------------------------------|--------------------------------------------------------------|-----|-----|-----|-------|-------|

| Supply Current (I <sub>dd</sub> )    | V <sub>DD</sub> = 1.8 V, no load<br>f <sub>swclk</sub> = Off |     | 9   |     | μA    | 4     |

| Supported Data Rates                 |                                                              |     |     |     |       |       |

| Data Rate, Port 1 fDATA1             | Disabled                                                     |     |     |     |       |       |

| Data Rate, Port 2 f <sub>DATA2</sub> | Disabled                                                     |     |     |     |       |       |

| Control                              | Active                                                       |     |     |     |       |       |

Note 4: Mode 2-2 (Clock Stop) is notified through the SoundWire bus. When the clock restarts, the microphone will immediately enter Idle 1 Mode for ClockStopMode=0 OR re-sync and re-enumerate for ClockStopMode=1.

#### TABLE 7. ACOUSTICAL/ELECTRICAL CHARACTERISTICS - MODE 3-1 (SYNC AND ENUMERATION)

T<sub>A</sub> = 25°C, VDD = 1.8 V, C<sub>LOAD</sub> = 60 pF unless otherwise noted. Typical specifications are not guaranteed

| PARAMETER                            | CONDITIONS                                  | MIN  | ТҮР | MAX  | UNITS | NOTES |

|--------------------------------------|---------------------------------------------|------|-----|------|-------|-------|

|                                      | V <sub>DD</sub> = 1.8 V, no load            |      |     |      |       |       |

| Supply Current (Is)                  | f <sub>swclk</sub> = 0.6MHz (assumes mic id |      | 350 |      | μΑ    | 7     |

|                                      | 1 and 0 only)                               |      |     |      |       |       |

| Acoustical/Electrical Specifications |                                             |      |     |      |       |       |

| No Signal                            |                                             |      |     |      |       |       |

| Supported Data Rates                 |                                             |      |     |      |       |       |

| Data Rate, Port 1 f <sub>DATA1</sub> | Disabled                                    |      |     |      |       |       |

| Data Rate, Port 2 f <sub>DATA2</sub> | Disabled                                    |      |     |      |       |       |

| Control                              | Active                                      |      |     |      |       |       |

| Enumeration Control                  |                                             |      |     |      |       |       |

| Unique ID = 0                        | IDSEL pin state: Tied to GND                |      | 0   |      | Ω     | 5,6   |

| Unique ID = 1                        | IDSEL pin state: Tied to VDD                |      | 0   |      | Ω     | БС    |

|                                      | (max 1.98V)                                 |      |     |      |       | 5,6   |

| Unique ID = 2                        | IDSEL pin state: Resistor to GND            | 25.7 | 27  | 28.3 | kΩ    | 5,6   |

| Unique ID = 3                        | IDSEL pin state: Resistor to GND            | 14.3 | 15  | 15.7 | kΩ    | 5,6   |

| Unique ID = 4                        | IDSEL pin state: Resistor to GND            | 7.8  | 8.2 | 8.6  | kΩ    | 5,6   |

| Unique ID = 5                        | IDSEL pin state: Resistor to GND            | 4.1  | 4.3 | 4.5  | kΩ    | 5,6   |

| Unique ID = 6                        | IDSEL pin state: Resistor to GND            | 2.1  | 2.2 | 2.3  | kΩ    | 5,6   |

| Tolerance of resistors               |                                             |      | ± 5 |      | %     |       |

**Note 5:** Unique ID refers to the 4 LSB bits in the SCP\_DevID\_0 register.

**Note 6:** Up to 7 T5808 slave devices can be configured by a single SoundWire master. See Sync & Enumeration section for details on slave enumeration. **Note 7:** Guaranteed by design

#### TABLE 8. ACOUSTICAL/ELECTRICAL CHARACTERISTICS – MODE 4-1 (POWER OFF, CLOCK ON)

T<sub>A</sub> = 25°C, VDD = 1.8 V, C<sub>LOAD</sub> = 60 pF unless otherwise noted. Typical specifications are not guaranteed.

| PARAMETER                            | CONDITIONS | MIN | ТҮР      | MAX | UNITS | NOTES |

|--------------------------------------|------------|-----|----------|-----|-------|-------|

| Supply Voltage (VDD)                 |            |     |          | 1.2 | V     |       |

| Supply Current (Idd)                 | No load    |     |          | 9   | μA    |       |

| Acoustical/Electrical Specifications |            |     |          |     |       |       |

| No Signal                            |            |     |          |     |       |       |

| Supported Data Rates                 |            |     |          |     |       |       |

| Data Rate, Port 1 fDATA1             | Any Clock  |     | Disabled |     | Mbps  |       |

| Data Rate, Port 2 fDATA2             | Any Clock  |     | Disabled |     | Mbps  |       |

| Control                              | Inactive   |     |          |     |       |       |

#### TABLE 9. ACOUSTICAL/ELECTRICAL CHARACTERISTICS - MODE 4-2 (POWER OFF, CLOCK OFF)

$T_A = 25^{\circ}$ C, VDD = 1.8 V, C<sub>LOAD</sub> = 60 pF unless otherwise noted. Typical specifications are not guaranteed.

| PARAMETER                            | CONDITIONS                               | MIN | ТҮР | MAX | UNITS | NOTES |

|--------------------------------------|------------------------------------------|-----|-----|-----|-------|-------|

| Supply Voltage (V <sub>DD</sub> )    |                                          |     |     | 1.2 | V     |       |

| Supply Current (Idd)                 | No load<br>f <sub>swclk</sub> = max 1kHz |     |     | 9   | μΑ    |       |

| Acoustical/Electrical Specifications |                                          |     |     |     |       |       |

| Supported Data Rates                 |                                          |     |     |     |       |       |

| Data Rate, Port 1 f <sub>DATA1</sub> | Disabled                                 |     |     |     |       |       |

| Data Rate, Port 2 f <sub>DATA2</sub> | Disabled                                 |     |     |     |       |       |

| Control                              | Inactive                                 |     |     |     |       |       |

#### TABLE 10. ACOUSTICAL/ELECTRICAL CHARACTERISTICS - MODE 4-3 (POWER ON, CLOCK OFF)

T<sub>A</sub> = 25°C, VDD = 1.8 V, C<sub>LOAD</sub> = 60 pF unless otherwise noted. Typical specifications are not guaranteed.

| PARAMETER                            | CONDITIONS                    | MIN | ТҮР | MAX  | UNITS | NOTES |

|--------------------------------------|-------------------------------|-----|-----|------|-------|-------|

| Supply Voltage (VDD)                 |                               | 1.5 | 1.8 | 1.98 | V     |       |

|                                      |                               |     |     |      |       |       |

| Supply Current (Idd)                 | No load                       |     | 9   |      | μΑ    |       |

|                                      | f <sub>swclk</sub> = max 1kHz |     |     |      |       |       |

| Acoustical/Electrical Specifications |                               |     |     |      |       |       |

| No Signal                            |                               |     |     |      |       |       |

| Supported Data Rates                 |                               |     |     |      |       |       |

| Data Rate, Port 1 fDATA1             | Disabled                      |     |     |      |       |       |

| Data Rate, Port 2 fDATA2             | Disabled                      |     |     |      |       |       |

| Control                              | Inactive                      |     |     |      |       |       |

#### **TABLE 11. MODE TRANSITION TIMES**

$T_A = 25^{\circ}$ C, VDD = 1.8 V,  $C_{LOAD} = 60$  pF unless otherwise noted. All transition times are from simulation and are typical specifications which are not guaranteed.

|      |     |        |        |        | TON    | <b>IODE</b> |        |        |        |        |

|------|-----|--------|--------|--------|--------|-------------|--------|--------|--------|--------|

|      |     | 1-1    | 1-2    | 1-3    | 1-4    | 2-2         | 3-1    | 4-1    | 4-2    | 4-3    |

|      | 1-1 |        |        | 100 µs | 100 µs | 100 µs      |        | 100 µs | 100 µs | 100 µs |

| ЭE   | 1-2 |        |        | 100 µs | 100 µs | 100 µs      |        | 100 µs | 100 µs | 100 µs |

| MODE | 1-3 | 100 µs | 100 µs |        | 100 µs | 100 µs      |        | 100 µs | 100 µs | 100 µs |

| 2    | 1-4 | 10 ms  | 10 ms  |        |        | 100 µs      |        | 100 µs | 100 µs | 100 µs |

| FROM | 2-2 |        |        |        | 100 µs |             | 100 µs | 100 µs | 100 µs | 100 µs |

| ш    | 3-1 |        |        |        | 100 µs |             |        | 100 µs | 100 µs | 100 µs |

|      | 4-1 |        |        |        |        |             |        |        |        |        |

|      | 4-2 |        |        |        |        |             |        |        |        |        |

|      | 4-3 |        |        |        |        |             |        |        |        |        |

Greyed out cells are either same mode, not allowed, or not specified

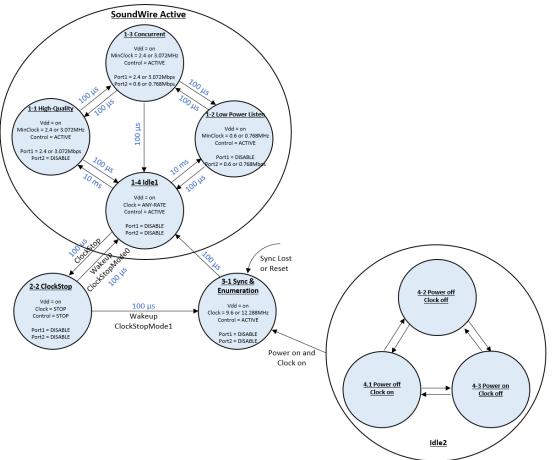

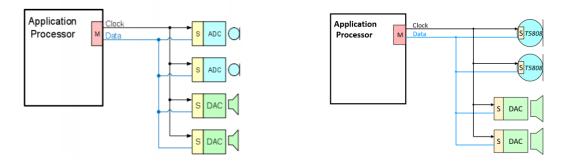

Figure 1. State transition diagram of available modes on T5808, transition time conditions described in Table 11.

#### **TABLE 12. DIGITAL INPUT/OUTPUT CHARACTERISTICS**

T<sub>A</sub> = 25°C, 1.62V < VDD < 1.98V, unless otherwise noted.

| PARAMETER                              | CONDITIONS                  | MIN                  | ТҮР             | MAX                  | UNITS | NOTES |

|----------------------------------------|-----------------------------|----------------------|-----------------|----------------------|-------|-------|

| Input Voltage High (V <sub>IH</sub> )  |                             | $0.65 \times V_{DD}$ |                 |                      | V     |       |

| Input Voltage Low (V <sub>IL</sub> )   |                             |                      |                 | $0.35 \times V_{DD}$ | V     |       |

| Output Voltage High (V <sub>OH</sub> ) | $I_{LOAD} = 0.5 \text{ mA}$ | $0.7 \times V_{DD}$  | V <sub>DD</sub> |                      | V     |       |

| Output Voltage Low (V <sub>OL</sub> )  | I <sub>LOAD</sub> = 0.5 mA  |                      | 0               | $0.3 \times V_{DD}$  | V     |       |

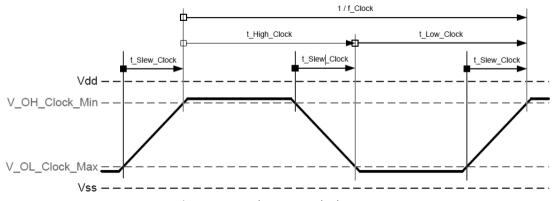

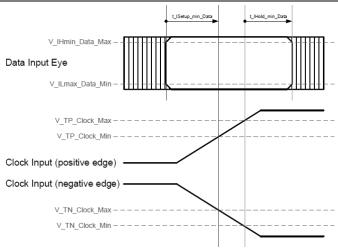

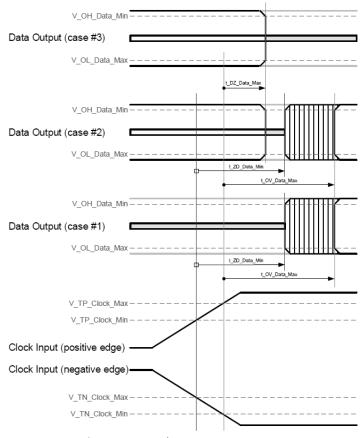

#### TABLE 13. DIGITAL (PHY) INPUT/OUTPUT TIMING CHARACTERISTICS

T<sub>A</sub> = 25°C, 1.7V < VDD < 1.9V, unless otherwise noted.

| PARAMETER                        | CONDITIONS                                          | MIN   | ТҮР | MAX    | UNITS | NOTES |

|----------------------------------|-----------------------------------------------------|-------|-----|--------|-------|-------|

| f <sub>swclk</sub>               | Input clock frequency                               | 0.024 |     | 12.288 | MHz   |       |

| t <sub>CLKIN</sub> (t_1/f_Clock) | Input clock period                                  | 81    |     | 41,666 | ns    |       |

| t_Slew_Clock                     | Clock Slew Time                                     | 2     |     | 5.4    | ns    |       |

| Clock Duty Cycle                 | f <sub>SWCLK</sub> < 12.288MHz                      | 45    | 50  | 55     | %     |       |

| t_ISetup_min_Data                | Data input setup time                               |       |     | 0      | ns    | 7     |

| t_IHold_min_Data                 | Data input hold time                                |       |     | 4      | ns    | 7     |

| t_ZD_Data_Min                    | Data output enable time from initial clock edge     | 7.9   |     |        | ns    |       |

| t_DZ_Data_Max                    | Data output disable time from subsequent clock edge |       |     | 4      | ns    |       |

| t_OV_Data_Max                    | Data output valid time                              |       |     | 27.9   | ns    |       |

Note 7: Guaranteed by design

Figure 2. Digital Timing – Clock Output

# SOUNDWIRE OVERVIEW

The following section provides an overview of SoundWire. For the detailed SoundWire spec, please review the MIPI SoundWire specification document.

SoundWire microphones provide an interface to transport both audio and control over a pin efficient interface. In older microphone interfaces, the control portion has either been provided by separate pin, interpreted from the audio bus or power supply pins, or not supported – leading to a limited ability to control microphone behavior. The ability of SoundWire microphones to control the microphone from a centralized point in the audio subsystem enables better overall functionality and the following features:

- Control of power mode of each microphone in the system using an explicit control instead of implicit control using power or clock pins.

- Transition between Low Power Listen mode and High Quality mode without interruption for continuous audio use cases (i.e. low-power voice activation).

The SoundWire interface provides the following key capabilities:

- Transport of the following over a single two-pin interface:

- Payload data channels

- Each slave microphone has 2 data ports. Depending on how the SoundWire devices are configured, a microphone on the bus can operate in High Quality mode, Low Power Listen mode or both.

- Control information

- Setup commands

- Support for microphone low latency PDM audio transport over the same link with other audio sources

- Support for multilevel power saving by enabling frequency changes, temporary clock stoppage, and wake up response to inband signaling

- Active indication of microphone device status including interrupt-style alerts

#### **T5808 SOUNDWIRE MICROPHONE**

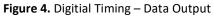

The T5808 is a SoundWire v1.1 fully compatible microphone. It connects directly to the SoundWire bus without the need for an intermediary SoundWire ADC or Codec, as shown in the figure below. The T5808 is configured as a SoundWire slave, where the Application Processor operates as the SoundWire master, with the ability to control the mic and access its Payload data through the SoundWire data stream.

**Figure 5.** MIPI Example Microphone Topology (left) includes SoundWire ADC. T5808 digital mic with integrated SoundWire Slave functionality connects directly to the SoundWire bus without need for ADC (right).

The audio captured by the T5808 is a low latency PDM bitstream which is transmitted in the Payload of the SoundWire data stream. The T5808 can transmit data from both of its dataports, High Quality Mode and Low Power Listen Mode, simultaneously in the same Payload. This means the SoundWire bus can contain data from multiple T5808 dataports across multiple T5808 microphones, as well as data from other SoundWire devices on the same bus. The T5808 has 7 unique device ID (IDSEL) configurations, allowing connection of up to 7 T5808 SoundWire Microphone Slaves on a single SoundWire bus.

T5808 SoundWire features:

- SoundWire v1.1 slave

- Basic PHY device

- 1.8V signal support

- 7 unique microphones on the system

#### ATTACHING TO SOUNDWIRE AND TRANSMITTING AUDIO

In order to transmit audio on the SoundWire bus, the T5808 needs to be established (attached) as a SoundWire slave on the bus, set up a data port and then start sending audio data on the data port. This involves transition across three defined modes in the SoundWire protocol:

- 3-1 Sync&Eumeration

- 1-4 Idle1

- 1-1 High Quality <u>OR</u> 1-2 Low Power Listen

Figure 6. State transitions during start up

#### SYNC AND ENUMERATION

The T5808 is established as a slave on the SoundWire bus in the Sync And Enumeration mode. On entering the mode the following conditions exist:

- Vdd is on

- SoundWire CLK is on

- T5808 is not attached

- SoundWire has not enumerated the device

- Audio channels are disabled

The T5808 attaches itself as a SoundWire slave by:

- Frame Synchronization: It syncs with the control word within the control portion of the frame with the default device id = 0.

- Slave Enumeration: The master gives it a unique device id to distinguish from the other slaves on the bus.

#### IDLE1

After enumeration has been successfully carried out the microphone enters Idle1 mode. On entering the mode the following conditions exist:

- Vdd is on

- SoundWire CLK is on

- T5808 is attached

- SoundWire has enumerated the device

- Audio channels are disabled

Before audio data can be sent on the SoundWire bus, a Data Port needs to be set up on the device. A Data Port is a subset of a device that is either a source or sink of one Payload Stream on the SoundWire bus. On the T5808 there are two Data Ports

implemented - Data Port 1 and Data Port 2, for High Quality and Low Power Listen modes respectively. The Data Port has to be configured with the necessary information to describe how the Payload data is organized within a SoundWire frame. This information includes:

- Data Type

- Sample Length

- Sample Interval

- HStart and HStop

- Offset

- Word Length

#### **TRANSMITTING AUDIO (HQM OR LPLM)**

When a Data Port has been enabled (Data Port 1 or 2), the mic exits Idle1 mode and enters HQM or LPLM (depending on which is selected) and the audio data captured by the microphone will become active on the SoundWire data bus in the form of a PDM bitstream. The data rate of the bitstream will be determined by the SoundWire clock and the Sample Interval as outlined in the *Frame Structure* section. For HQM this is 2.4Mbps or 3.072Mbps, and for LPLM it is 0.6Mbps or 0.768Mbps. It is possible to leave HQM or LPLM and go back into Idle1 mode at any time.

The HQM and LPLM, and therefore Data Ports 1 and 2, can both be active at the same time in Concurrent mode. However either one of HQM or LPLM have to be established first, before the other mode is added. When in Concurrent mode, it is possible to leave and go back to either HQM or LPLM. It is also possible in Concurrent mode to go directly to Idle1 mode without having to transition to HQM or LPLM first.

Figure 7. State transition options when the Data Port has been established and the audio stream is up and running

#### **CONCURRENT MODE**

In Concurrent Mode the microphone simultaneously outputs HQM and LPLM audio streams on Data Port 1 and Data Port 2 respectively. It can be used to minimize interruption in transitioning from LPLM to HQM and back to LPLM again, by operating as an intermediate mode. By allowing the datastreams to overlap, the SoundWire Master can extract each data stream and stitch together a single uninterrupted audio stream. Concurrent Mode can also be used to provide independent audio streams where two simultaneous applications need LPLM and HQM respectively. Concurrent mode is enabled by the SoundWire capability to output multiple audio data streams at different data rates.

| MODE NAME        | MODE NUMBER | PORT 1   | PORT 2   | PDM RATE                       |

|------------------|-------------|----------|----------|--------------------------------|

| High Quality     | 1-1         | Enabled  | Disabled | 2.4Mbps, 3.072Mbps             |

| Low Power Listen | 1-2         | Disabled | Enabled  | 0.6Mbps, 0.768Mbps             |

| Concurrent       | 1-3         | Enabled  | Enabled  | 0.6/2.4Mbps or 0.768/3.072Mbps |

#### **TABLE 14. AVAILABLE MODES AND DATA RATES**

#### FRAME STRUCTURE

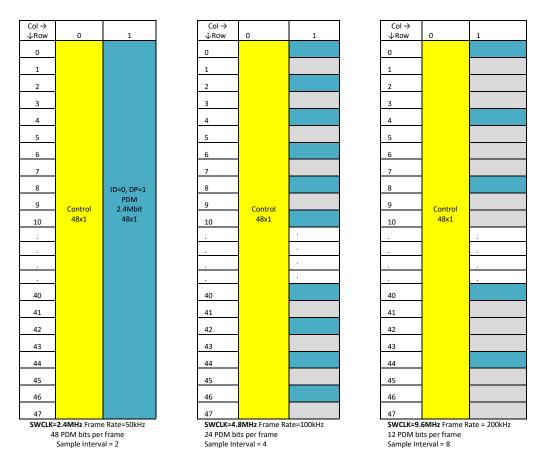

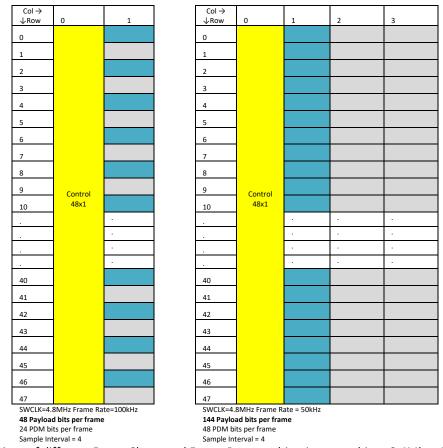

The SoundWire bitstream is a continuous stream of bits encoded using the modified-NRZI scheme, but for organizational purposes it is conceptually divided into a repetive sequence of bits to form a frame structure. This section focuses on the organization of the frame structure in order to achieve the desired SoundWire Clock, Frame Size and audio Data Rate. Note the T5808 can send and receive Control data in the data frame but it only sends Payload data as it since it is an audio input device to the Master.

The frame is constructed as a two dimensional array of bit slots, with 48 to 256 rows and 2 to 16 columns. The Control data is always contained in the Control Word which is the first 48 rows of the first column. The number of rows and columns is configurable to provide flexibility in creating an efficient data frame to multiplex data from multiple sources.

Some examples of a 48x2 frame are shown below. It shows the Control Word contained in row 0-47, col 0, per the MIPI spec. The Payload data is contained in row 0-47, col1, is generated by the T5808, ID=0, DataPort=1 (High Quality Mode) which is 2.4Mbit PDM data. The three examples show how the same Payload data (2.4Mbit PDM) is transmitted over different SoundWire clocks 2.4MHz, 4.8MHz and 9.6MHz, while the Frame Size remains constant at 96 bits and the Frame Rate scales accordingly. The Frame Rate can be calculated from the SoundWire Clock and the Frame Size:

Frame Rate = SWCLK\*2/Frame Size

The sample interval of the PDM bitstream also scales with the SoundWire Clock and Frame Rate:

#### Sample Interval = SWCLK\*2/PDM Data Rate

(Note: Sample Interval must be greater than 1 to allow for Control Word bits)

In the examples below, the Frame Rate increases from 50kHz to 100kHz to 200kHz as SoundWire Clock increases from 2.4Mhz, 4.8MHz and 9.6MHz. Likewise the Sample Interval Increases from 2 to 4 to 8 to keep the PDM data rate constant. By increasing the SoundWire clock rate (and sample interval), more unused data bit slots become available for other bitstreams to use.

Figure 8. Comparison of different Sample Interval and Frame Rate combinations to achieve 2.4Mbps PDM Payload data

The SoundWire clock should be fast enough to run the highest desired data rate for the bitstream within the Payload. For PDM data at 3.072, 2.4, 0.768 and 0.6Mbps. See Table 15 below for more details.

|               | Data          | Port 1          | Data          | Port 2          |

|---------------|---------------|-----------------|---------------|-----------------|

| SoundWire CLK | PDM Data Rate | Sample Interval | PDM Data Rate | Sample Interval |

| 12.288MHz     | 3.072Mbps     | 8               | 0.768Mbps     | 32              |

| 9.600MHz      | 2.400Mbps     | 8               | 0.600Mbps     | 32              |

| 6.144MHz      | 3.072Mbps     | 4               | 0.768Mbps     | 16              |

| 4.800MHz      | 2.400Mbps     | 4               | 0.600Mbps     | 16              |

| 3.072Mhz      | 3.072Mbps     | 2               | 0.768Mbps     | 8               |

| 2.400MHz      | 2.400Mbps     | 2               | 0.600Mbps     | 8               |

| 1.536MHz      | Min 2.4Mbps   | N/A             | 0.768Mbps     | 4               |

| 1.200MHz      | Min 2.4Mbps   | N/A             | 0.600Mbps     | 4               |

| 0.768MHz      | Min 2.4Mbps   | N/A             | 0.768Mbps     | 2               |

| 0.600MHz      | Min 2.4Mbps   | N/A             | 0.600Mbps     | 2               |

#### TABLE 15. AVAILABLE CLOCK AND DATA RATE COMBINATIONS

Greyed out cells are not valid combinations of SoundWire CLK and Data Port PDM data rates

A larger frame size will also increase the number of available data bits without changing the SoundWire clock rate. The Frame Rate will scale accordingly as shown below:

Figure 9. Comparison of different Frame Shape and Frame Rate combinations to achieve 2.4Mbps PDM Payload data

# CONTROL WORD

In a similar fashion to the Frame structure, the Control data bits are conceptually organized into a Control Word of 48 bit data. The Control Word is not a continuous sequence of bits since it is interleaved by Payload data, however a word is an effective concept of organizing the control data. The 48 bits in the Control Word are assigned into the following categories:

- Control bits (20) from the Master that keep all interfaces synchronized to the Frame structure

- Command bits (28) from the Master or Monitor with corresponding response bits from the Slave or Master

Within the Command bits are bits which determine the device address, dataport and register for a specific command. SoundWire can write to all devices on the bus, individual device types on the bus or individual devices on the bus.

SoundWire provides a DeviceID[47:0] in the SCP\_DevID\_0 to SCP\_DevID\_5 registers that is read by the SoundWireMaster to identify the connected SoundWire slave device. The SoundWire slave DeviceID bits contains bit fields for:

- SoundWire Version (1.1 on this device)[47:44]

- Manufacturer ID [39:32]

- Part ID [23:16]

- Unique ID [43:40]

These fields are fixed except for the slave Unique ID which is pin configurable via the IDSEL pin and has seven possible combinations as shown in Table 7.

#### SOUNDWIRE REGISTER MAP

The SoundWire register map contains address blocks for the control port and the data ports. On T5818 the base address of the register is defined by whether it is Control Port, DataPort 1 or DataPort 2 as shown in the Table 16 below:

| Base Address | Port Name    | Prefix for    | Notes                                                |

|--------------|--------------|---------------|------------------------------------------------------|

| Range        |              | Register Name |                                                      |

| 0x00000000 - | Control Port | SCP_          | Control and status functions common to the whole     |

| 0x000000FF   |              |               | Device.                                              |

| 0x00000100 - | Data Port 1  | DP1_          | Control and status functions specific to Data Port 1 |

| 0x000001FF   |              |               |                                                      |

| 0x00000200 - | Data Port 2  | DP2_          | Control and status functions specific to Data Port 2 |

| 0x000002FF   |              |               |                                                      |

#### TABLE 16. ADDRESS RANGES FOR EACH DATA PORT

The register read/write is based on the base address shown above, along with the register specific offset as shown in Table 17, Table 18 and Table 19. The offset may have two options if it is banked for Bank 0 or Bank 1. Banks of Registers are used as a mechanism to make seamless changes to operation when those changes involve updating parameters in several registers in a device, or registers in several devices.

For detailed register and bit field descriptions, reference the full MIPI SoundWire<sup>®</sup> Specification (Version 1.1). T5808 uses a simplified data port therefore there are certain optional registers and the accompanying transport features are not implemented.

#### TABLE 17. SOUNDWIRE REGISTER ADDRESS MAP

| Base Address = |               | SISTER ADDRESS MAP             | an                   |                                                                                                                  |

|----------------|---------------|--------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------|

| Bank Type / Ad |               | Name                           | Access               | Notes                                                                                                            |

| Non-Banked     |               |                                | Access               | Notes                                                                                                            |

| + 0x00 - 0x3F  |               | Reserved                       | None                 | Optional Data Port 0 not implemented                                                                             |

| + 0x40         |               | SCP IntStat 1                  | RO                   | and the second |

| + 0x40         |               | SCP IntClear 1                 | WO                   |                                                                                                                  |

| + 0x41         |               | SCP IntMask 1                  | RW                   |                                                                                                                  |

| + 0x42         |               | SCP IntStat 2                  | RO                   |                                                                                                                  |

| + 0x43         |               | SCP IntStat 3                  | RO                   |                                                                                                                  |

| + 0x44         |               | SCP Ctrl                       | WO                   |                                                                                                                  |

| + 0x44         |               | SCP Stat                       | RO                   |                                                                                                                  |

| + 0x45         |               | SCP_SystemCtrl                 | RW                   |                                                                                                                  |

| + 0x46         |               | SCP DevNumber                  | RW                   |                                                                                                                  |

| + 0x47         |               | SCP_High-PHY_Check             | RW                   | Optional register not implemented                                                                                |

| + 0x48         |               | SCP AddrPage1                  | RW                   | Optional register not implemented                                                                                |

| + 0x49         |               | SCP_AddrPage2                  | RW                   | Optional register not implemented                                                                                |

| + 0x4A         |               | SCP KeeperEn                   | RW                   |                                                                                                                  |

| + 0x4B         |               | SCP BankDelay                  | RW                   | Optional register not implemented                                                                                |

| + 0x4C - 0x4E  |               | Reserved                       | None                 |                                                                                                                  |

| + 0x4F         |               | SCP TestMode                   | WO                   | Optional register not implemented                                                                                |

| + 0x50         |               | SCP Devid 0                    | RO                   |                                                                                                                  |

| + 0x51         |               | SCP Devid 1                    | RO                   |                                                                                                                  |

| + 0x52         |               | SCP Devid 2                    | RO                   |                                                                                                                  |

| + 0x53         |               | SCP Devid 3                    | RO                   |                                                                                                                  |

| + 0x54         |               | SCP Devid 4                    | RO                   |                                                                                                                  |

| + 0x55         |               | SCP Devid 5                    | RO                   |                                                                                                                  |

| + 0x56 – 0x5F  |               | Reserved                       | None                 |                                                                                                                  |

| Bank 0         | Bank 1        |                                |                      |                                                                                                                  |

| + 0x60         | + 0x70        | SCP FrameCtrl                  | wo                   |                                                                                                                  |

| + 0x61         | + 0x71        | SCP NextFrame                  | WO                   | Optional registers not implemented                                                                               |

| + 0x62 – 0x6F  | + 0x72 – 0x7F | Reserved                       | None                 |                                                                                                                  |

| Non-Banked     |               |                                |                      |                                                                                                                  |

| + 0x80 – 0xFF  |               | Reserved                       | None                 |                                                                                                                  |

| Base Address = | = 0x00000100  | Data Port 1 Register Map       |                      |                                                                                                                  |

| Base Address = |               | Data Port 2 Register Map       |                      |                                                                                                                  |

|                |               | Registers referenced as DPn, w | vhere <i>n</i> = 1 o | or 2                                                                                                             |

| Bank Type / Ad | ddress Offset | Name                           | Access               | Notes                                                                                                            |

| Non-Banked     |               | 1                              |                      |                                                                                                                  |

| + 0x00         |               | DPn IntStat                    | RO                   |                                                                                                                  |

| + 0x00         |               | <br>DPn_IntClear               | WO                   |                                                                                                                  |

| + 0x01         |               | DPn_IntMask                    | RW                   |                                                                                                                  |

| + 0x02         |               | DPn_PortCtrl                   | RW                   |                                                                                                                  |

| + 0x03         |               | DPn_BlockCtrl1                 | RW                   |                                                                                                                  |

| + 0x04         |               | DPn_PrepareStatus              | RO                   | Feature not implemented (register can be read)                                                                   |

| + 0x05         |               | DPn_PrepareCtrl                | RW                   | Feature not implemented<br>Write response – 'Command Ignored'                                                    |

| 0.00 0.45      |               |                                |                      | Read response – ACK=1, data = 0x3F                                                                               |

| + 0x06 – 0x1F  |               | Reserved                       | None                 |                                                                                                                  |

| Bank 0         | Bank 1        |                                |                      |                                                                                                                  |

| + 0x20         | + 0x30        | DPn_ChannelEn                  | RW                   |                                                                                                                  |

| + 0x21         | + 0x31        | DPn_BlockCtrl2                 | RW                   | Not Required in Simplified Data Port                                                                             |

| + 0x22         | + 0x32        | DPn_SampleCtrl1                | RW                   |                                                                                                                  |

# **公TDK**

# **T5808**

|                |               |                                  |            | 1                                    |

|----------------|---------------|----------------------------------|------------|--------------------------------------|

| + 0x23         | + 0x33        | DPn_SampleCtrl2                  | RW         | Not Required in Simplified Data Port |

| + 0x24         | + 0x34        | DPn_OffsetCtrl1                  | RW         |                                      |

| + 0x25         | + 0x35        | DPn_OffsetCtrl2                  | RW         | Not Required in Simplified Data Port |

| + 0x26         | + 0x36        | DPn_HCtrl                        | RW         | Not Required in Simplified Data Port |

| + 0x27         | + 0x37        | DPn_BlockCtrl3                   | RW         | Not Required in Simplified Data Port |

| + 0x28         | + 0x38        | DPn_LaneCtrl                     | RW         | Conditional per multi-lane           |

| + 0x29 – 0x2F  | + 0x39 – 0x3F | Reserved                         | None       |                                      |

| Non-Banked     |               |                                  | -          |                                      |

| + 0x40 – 0xFF  |               | Reserved                         | None       |                                      |

| Base Address = | 0x00000300    | Data Ports 3 to 14 Register Map  | -          |                                      |

| + 0x000 – 0xBF | F             | Reserved                         | None       | Ports 3 to 14 are not implemented    |

| Base Address = | 0x00000F00    | All Payload Ports Register Addre | ss Aliases |                                      |

| Bank Type / Ad | dress Offset  | Name                             | Access     | Notes                                |

| Non-Banked     |               |                                  |            |                                      |

| + 0x00         |               | DP_All_P_IntStat                 | RO         |                                      |

| + 0x00         |               | DP_All_P_IntClear                | WO         |                                      |

| + 0x01         |               | DP_All_P_IntMask                 | RW         |                                      |

| + 0x02         |               | DP_All_P_PortCtrl                | RW         |                                      |

| + 0x03         |               | DP_All_P_BlockCtrl1              | RW         |                                      |

| + 0x04         |               | DP_All_P_PrepareStatus           | RO         |                                      |

| + 0x05         |               | DP_All_P_PrepareCtrl             | RW         |                                      |

| + 0x06 – 0x1F  |               | Reserved                         | None       |                                      |

| Bank 0         | Bank 1        |                                  |            |                                      |

| + 0x20         | + 0x30        | DP_All_P_ChannelEn               | RW         |                                      |

| + 0x21         | + 0x31        | DP_All_P_BlockCtrl2              | RW         | Not Required in Simplified Data Port |

| + 0x22         | + 0x32        | DP_All_P_SampleCtrl1             | RW         |                                      |

| + 0x23         | + 0x33        | DP_All_P_SampleCtrl2             | RW         | Not Required in Simplified Data Port |

| + 0x24         | + 0x34        | DP_All_P_OffsetCtrl1             | RW         |                                      |

| + 0x25         | + 0x35        | DP_All_P_OffsetCtrl2             | RW         | Not Required in Simplified Data Port |

| + 0x26         | + 0x36        | DP_All_P_HCtrl                   | RW         | Not Required in Simplified Data Port |

| + 0x27         | + 0x37        | DP_All_P_BlockCtrl3              | RW         | Not Required in Simplified Data Port |

| + 0x28         | + 0x38        | DP_All_P_LaneCtrl                | RW         | Conditional per multi-lane           |

| + 0x29 – 0x2F  | + 0x39 – 0x3F | Reserved                         | None       |                                      |

| Base Address = | 0x00003000    | Implementation Defined Registe   | ers (DDC)  |                                      |

| Bank Type / Ad | dress Offset  | Name                             | Access     | Notes                                |

| Non-Banked     |               |                                  |            |                                      |

| + 0x00         |               | DDC_Overall_Capability_List      | RO         |                                      |

| + 0x01         |               | DDC_Mic_Directivity              | RO         |                                      |

| + 0x02         |               | DDC_Mic_Min_Sensitivity          | RO         |                                      |

| + 0x03         |               | DDC_Mic_Max_Sensitivity          | RO         |                                      |

| + 0x04         |               | DDC_Mic_AOP                      | RO         |                                      |

| + 0x05         |               | DDC_MIC_MAX_AOP                  | RO         |                                      |

| + 0x06         |               | DDC_Mic_Clock_Sources            | RO         |                                      |

| + 0x07         |               | DDC_Mic_Change_Audio_Rate        | RO         |                                      |

| + 0x08         |               | DDC_Mic_Min_HPF_Freq             | RO         |                                      |

| + 0x09         |               | DDC_Mic_Max_HPF_Freq             | RO         |                                      |

| + 0x0A         |               | DDC_Mic_Ultrasound_Rates         | RO         |                                      |

| + 0x0B         |               | IO PAD Control                   | RW         |                                      |

# **公TDK** SOUNDWIRE REGISTER DEFINITIONS

#### **TABLE 18. SLAVE CONTROL PORT REGISTERS**

### SCD INITSTAT 1 / SCD INITCLEAD 1

| ScP_INTSTAT_1 / SCP_INTCLEAR_1 ADDRESS |   |         |         |   |   |           |        |         |

|----------------------------------------|---|---------|---------|---|---|-----------|--------|---------|

| 7                                      | 6 | 5       | 4       | 3 | 2 | 1         | 0      | Default |

| -                                      | - | Port2   | Port1   | - | - | Bus Clash | Parity |         |

|                                        |   | Cascade | Cascade |   |   |           |        |         |

|                                        |   | R       | 0       |   |   | R/W1C     | R/W1C  |         |

| 0                                      | 0 | 0       | 0       | 0 | 0 | 0         | 0      | 0x00    |

| Bits | Name          | Function                                                                                      |

|------|---------------|-----------------------------------------------------------------------------------------------|

| 7:6  | -             | Reserved                                                                                      |

| 5:4  | Portn Cascade | Indicate whether at least one unmasked interrupt condition is set in the corresponding        |

|      | (n=1 or 2)    | DPn interrupt status register. Cleared by clearing the the source in the appropriate          |

|      |               | DPn interrupt status register.                                                                |

|      |               | 0 – No unmasked interrupt condion exists                                                      |

|      |               | 1 – At least one unmasked interrupt condition exists                                          |

| 3    | -             | Reserved                                                                                      |

| 2    | ImpDef1       | not implemented                                                                               |

| 1    | Bus Clash     | Indicates whether an interrupt is pending due to detection of a bus clash condition.          |

|      |               | Will generate an interrupt if the corresponding mask bit is set.                              |

|      |               | Writing a '1' to this bit position clears this condition along with the associated            |

|      |               | interrupt.                                                                                    |

|      |               | 0 – No bus clash detected                                                                     |

|      |               | 1 – Bus clash detected                                                                        |

| 0    | Parity        | Indicates whether a parity error has been detected on the bus. Will generate an               |

|      |               | interrupt if the the corresponding mask bit is set. Writing a '1' to this bit position clears |

|      |               | this condition along with the associated interrupt                                            |

|      |               | 0 – No parity error detected                                                                  |

|      |               | 1 – Parity error detected                                                                     |

#### ScP\_INTMASK\_1

ADDRESS BASE + 0X41 7 6 5 4 3 2 1 0 Default -Mask Mask Bus Clash Parity RW 0 0 0 0 0 0 0 0 0x00

| Bits | Name           | Function                                                                                                          |

|------|----------------|-------------------------------------------------------------------------------------------------------------------|

| 7:3  | -              | Reserved                                                                                                          |

| 2    | Mask ImpDef1   | not used because ImpDef1 is not implemented                                                                       |

| 1    | Mask Bus Clash | Determines whether a bus clash event generates an interrupt<br>0 – Bus clash does not generate an interrrupt      |

|      |                | 1 – Bus clash generates an interrupt                                                                              |

| 0    | Mask Parity    | Determines whether a parity error event generates an interrupt<br>0 – Parity error does not generate an interrupt |

|      |                | 1 – Parity error generates an interrupt                                                                           |

#### ADDRESS BASE + 0X42

| ScP_INTSTAT_ | SCP_INTSTAT_2 ADDRESS BAS |   |   |   |   |   |   |         |  |

|--------------|---------------------------|---|---|---|---|---|---|---------|--|

| 7            | 6                         | 5 | 4 | 3 | 2 | 1 | 0 | Default |  |

|              |                           |   |   |   |   | - | - |         |  |

|              | RO                        |   |   |   |   |   |   |         |  |

| 0            | 0                         | 0 | 0 | 0 | 0 | 0 | 0 | 0x00    |  |

| Bits | Name | Function |                         |

|------|------|----------|-------------------------|

| 7:0  | -    | Reserved | Always reads back a '0' |

#### ScP INTSTAT 3

| ScP_INTSTAT_ | SCP_INTSTAT_3 ADDRESS BAS |   |   |   |   |   |   |         |  |  |

|--------------|---------------------------|---|---|---|---|---|---|---------|--|--|

| 7            | 6                         | 5 | 4 | 3 | 2 | 1 | 0 | Default |  |  |

|              |                           |   |   |   |   | - | - |         |  |  |

|              | RO                        |   |   |   |   |   |   |         |  |  |

| 0            | 0                         | 0 | 0 | 0 | 0 | 0 | 0 | 0x00    |  |  |

| Bits | Name | Function |                         |

|------|------|----------|-------------------------|

| 7:0  | -    | Reserved | Always reads back a '0' |

#### ScP Ctrl / SCP Stat

| ScP_Ctrl / S | ScP_Ctrl / SCP_Stat Address Base + 0 |           |    |   |   |           |             |         |  |  |

|--------------|--------------------------------------|-----------|----|---|---|-----------|-------------|---------|--|--|

| 7            | 6                                    | 5         | 4  | 3 | 2 | 1         | 0           | Default |  |  |

| Force Rese   | t Current                            | High-PHY_ |    |   |   | ClockStop | ClockStop_  |         |  |  |

|              | Bank                                 | NotOK     |    |   |   | Now       | NotFinished |         |  |  |

| WO           | RO                                   |           | RO |   |   |           | RO          |         |  |  |

| 0            | 0                                    | 1         | 0  | 0 | 0 | 0         | 0           | 0x20    |  |  |

| Bits | Name                  | Function                                                             |                      |

|------|-----------------------|----------------------------------------------------------------------|----------------------|

| 7    | Force Reset           | Used to initiate a device reset                                      |                      |

|      |                       | 0 – No action                                                        |                      |

|      |                       | 1 – Force a device reset                                             |                      |

| 6    | CurrentBank           | Identifies the current register bank                                 |                      |

|      |                       | 0 – Current register bank is Bank 0                                  |                      |

|      |                       | 1 – Current register bank is Bank 1                                  |                      |

| 5    | High-PHY_NotOK        | High-PHY option not supported Alwa                                   | ays reads back a '1' |

| 4:2  | -                     | Reserved                                                             |                      |

| 1    | ClockStopNow          | Informs the slave that the master is stopping the SoundWire clock at | the end of the next  |

|      |                       | frame                                                                |                      |

|      |                       | 0 – Normal operation                                                 |                      |

|      |                       | 1 – SoundWire clock will stop at the end of the next frame           |                      |

| 0    | ClockStop_NotFinished | Indicates whether the device has completed any required shutdow      | n sequence and is    |

|      |                       | ready for SoundWire master to stop the SoundWire clock via assertion | ng ClockStopNow      |

|      |                       | 0 – Device is ready for a clock stop event                           |                      |

|      |                       | 1 – Device not finished with necessary clock stop state transitions  |                      |

#### ScP\_SYSTEMCTRL

#### ADDRESS BASE + 0X45

| 7  | 6 | 5 | 4         | 3      | 2         | 1 | 0         | Default |

|----|---|---|-----------|--------|-----------|---|-----------|---------|

|    |   |   | High-PHY_ | WakeUP | ClockStop |   | ClockStop |         |

|    |   |   | Select    | Enable | Mode      |   | Prepare   |         |

| RW |   |   |           |        |           |   |           |         |

| 0  | 0 | 0 | 0         | 0      | 0         | 0 | 0         | 0x00    |

| Bits | Name             | Function                                             |                         |

|------|------------------|------------------------------------------------------|-------------------------|

| 7:5  | -                | Reserved                                             |                         |

| 4    | High-PHY_Select  | Option not supported                                 | Always reads back a '0' |

| 3    | WakeUpEnable     | Feature not supported                                |                         |

| 2    | ClockStopMode    | It selects between ClockStopMode0 and ClockStopMode1 |                         |

| 1    | -                | Reserved                                             |                         |

| 0    | ClockStopPrepare | Feature not supported                                |                         |

#### ScP\_DEVNUMBER

#### ADDRESS BASE + 0X46

| 7       | 6 | 5    | 4     | 3             | 2 | 1 | 0    | Default |

|---------|---|------|-------|---------------|---|---|------|---------|

|         |   | Grou | ıp ID | Device Number |   |   |      |         |

| RW      |   |      |       |               |   |   |      |         |

| 0 0 0 0 |   |      | 0     | 0             | 0 | 0 | 0x00 |         |

| Bits | Name          | Function                                                                                                                                                                                                                                                                                                                                                                                                   |

|------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6  | -             | Reserved                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5:4  | Group ID      | <ul> <li>Indicates whether the device is addressable by a group alias in addition to being addressed by commands targeted to its own device number</li> <li>00 - Normal, not in a shared group</li> <li>01 - Group 12. The device responds to any commands directed to DevAddr = 12</li> <li>10 - Group 13. The device responds to any commands directed to DevAddr = 13</li> <li>11 - Reserved</li> </ul> |

| 3:0  | Device Number | Indicates the specific device number assigned to the device. This value is compared against the DevAddr field in the control world to determine if the command is targeted to this device.                                                                                                                                                                                                                 |

#### ScP\_KEEPEREN

#### ADDRESS BASE + 0X4A

|         |         |         |         |         |         |         | / (B B I ( 200 B) |         |

|---------|---------|---------|---------|---------|---------|---------|-------------------|---------|

| 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0                 | Default |

| KeepEN7 | KeepEN6 | KeepEN5 | KeepEN4 | KeepEN3 | KeepEN2 | KeepEN1 | Reserved          |         |

|         | RW      |         |         |         |         |         |                   |         |

| 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0                 | 0x00    |

| Bits | Name           | Function                                                |                  |

|------|----------------|---------------------------------------------------------|------------------|

| 7:1  | KeepENn, n=7:1 | Unused                                                  | Hardwired to '0' |

| 0    | Reserved       | Bus keeper is permanently disabled (single lane device) | Hardwired to '0' |

#### ScP\_DEVID\_0

#### ADDRESS BASE + 0X50

| 7                 | 6 | 5 | 4 | 3         | 2 | 1 | 0 | Default |

|-------------------|---|---|---|-----------|---|---|---|---------|

| SoundWire Version |   |   |   | Unique ID |   |   |   |         |

| RO                |   |   |   |           |   |   |   |         |

| 0                 | 0 | 1 | 0 | Х         | Х | Х | Х | 0x2X    |

| Bits | Name              | Function                                                                               |  |  |  |

|------|-------------------|----------------------------------------------------------------------------------------|--|--|--|

| 7:4  | SoundWire Version | Indicates which version of the MIPI SoundWire specification is supported by the device |  |  |  |

|      |                   | b0010 – SoundWire version 1.1                                                          |  |  |  |

|      |                   | These bits constitute DeviceID [47:44]                                                 |  |  |  |

| 3:0  | Unique ID         | Uniquely identifies the device if there are multiple instances of this device on the   |  |  |  |

|      |                   | SoundWire bus. See Sync & Enumeration section for operational details.                 |  |  |  |

|      |                   | These bits constitute DeviceID [43:40]                                                 |  |  |  |

#### ScP DEVID 1

| ScP_DEVID_1 |    |   |           |               |   |   | ADDRESS B | ASE + 0X51 |

|-------------|----|---|-----------|---------------|---|---|-----------|------------|

| 7           | 6  | 5 | 4         | 3             | 2 | 1 | 0         | Default    |

|             |    |   | Manufactu | rer ID [15:8] |   |   |           |            |

|             | RO |   |           |               |   |   |           |            |

| 0           | 0  | 0 | 0         | 0             | 0 | 1 | 0         | 0x02       |

| Bits | Name            | Function                                                                |  |

|------|-----------------|-------------------------------------------------------------------------|--|

| 7:0  | Manufacturer ID | Upper byte of the MIPI assigned manufacturers device ID                 |  |

|      |                 | These bits constitute DeviceID [39:32]. TDK's manufacturer id is 0x0235 |  |

#### ScP\_DEVID\_2

| ScP_DEVID_2 ADDRESS BA |    |   |           |              |   |   |   |         |

|------------------------|----|---|-----------|--------------|---|---|---|---------|

| 7                      | 6  | 5 | 4         | 3            | 2 | 1 | 0 | Default |

|                        |    |   | Manufactu | rer ID [7:0] |   |   |   |         |

|                        | RO |   |           |              |   |   |   |         |

| 0                      | 0  | 1 | 1         | 0            | 1 | 0 | 1 | 0x35    |

| Bits | Name            | Function                                                                |  |  |  |

|------|-----------------|-------------------------------------------------------------------------|--|--|--|

| 7:0  | Manufacturer ID | Lower byte of the MIPI assigned manufacturers device ID.                |  |  |  |

|      |                 | These bits constitute DeviceID [31:24]. TDK's manufacturer ID is 0x0235 |  |  |  |

| SCP_DEVID_3 ADDRESS BA |    |   |         |          |   |   |   |         |

|------------------------|----|---|---------|----------|---|---|---|---------|

| 7                      | 6  | 5 | 4       | 3        | 2 | 1 | 0 | Default |

|                        |    |   | Part ID | 0 [15:8] |   |   |   |         |

|                        | RO |   |         |          |   |   |   |         |

| 0                      | 1  | 0 | 1       | 1        | 0 | 0 | 0 | 0x58    |