# IAM-20680xx - WoM User Guide

InvenSense, Inc. reserves the right to change specifications and information herein without notice unless the product is in mass production and the application note has been designated by InvenSense in writing as subject to a specified Product / Process Change Notification Method regulation. InvenSense, a TDK Group Company 1745 Technology Drive, San Jose, CA 95110 U.S.A +1(408) 988–7339 invensense.tdk.com Document Number: AN-000409 Revision: 1.0 Date: 11/27/2023

## TABLE OF CONTENTS

| 1    | Purpose and scope                                  | .3 |  |

|------|----------------------------------------------------|----|--|

| 2    | Why Using Wake-on-Motion                           | .3 |  |

|      | Wake-on-motion enable sequence                     |    |  |

| 4    | Wake-on-Motion Configurations                      | .5 |  |

| 4.1. | . WoM triggering mode setting by accel_intel_mode5 |    |  |

|      | 4.1.1. ACCEL_INTEL_MODE[6] = 0                     | .5 |  |

|      | 4.1.2. ACCEL_INTEL_MODE[6] = 1                     | .6 |  |

| 4.2. | INT pin status latch7                              |    |  |

| 5    | Status register update8                            |    |  |

| 5.1. | . WOM flag bits detail8                            |    |  |

| 6    | Revision History                                   |    |  |

### **1** PURPOSE AND SCOPE

An application of TDK-InvenSense motion sensors is motion detection for low power operation of applications processor. The products of the IAM-20680xx 6-Axes family have a programmable interrupt system which can generate an interrupt signal on the INT pin. One of the interrupt system provides motion detection capability, Wake-on-Motion (WoM).

This document will explain the details on how to use WoM with IAM-20680xx and supplement to the WoM functions to provide the base understanding that customers need.

### 2 WHY USING WAKE-ON-MOTION

WoM detects motion when accelerometer data exceeds a programmable threshold. This motion event can be used to enable chip operation from sleep mode.

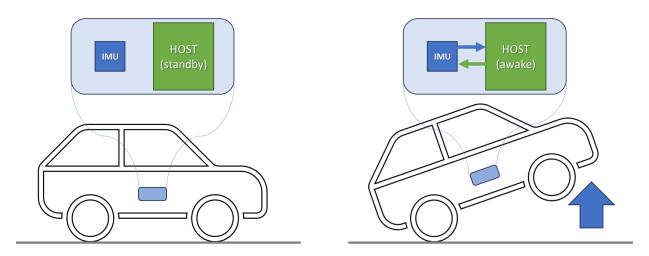

For example, a possible Automotive application (*theft-attempt detection*) is represented in Figure 1. When the car is parked, host processor generally wants to enter standby mode to save power consumption. In case of a theft attempt, car might be lifted, thus inducing an acceleration on any of the IMU axes. As a wake-event, if an acceleration is detected compared to any time frame, then IMU asserts interruption signal from INT pin as an event. By receiving the signal, HOST can be enabled and then can read IMU information or other processing can be implemented.

Figure 1. WOM mode for anti-theft application

### **3** WAKE-ON-MOTION ENABLE SEQUENCE

This section describes the necessary steps to enable WOM functionality in IAM-20680xx products. For details concerning the typical application schematic and necessary components, please refer to the product datasheet.

#### Step 1: Initialize all configurations

• In PWR\_MGMT\_1 register (0x6B) set DEVICE\_RESET = 1 (the bit will reset to 0 automatically)

#### Step 2: Ensure that Accelerometers, Gyroscopes and WOM function are disabled

- In PWR\_MGMT\_1 register (0x6B) set ACCEL\_CYCLE = 0

- In PWR\_MGMT\_2 register (0x6C) set STBY\_XA = STBY\_YA = STBY\_ZA = STBY\_XG = STBY\_YG = STBY\_ZG = 1

#### Step 3: Accelerometer Configuration

- In ACCEL\_CONFIG2 register (0x1D):

- set ACCEL\_FCHOICE\_B = 0 and A\_DLPF\_CFG[2:0] = b111

- > set DEC2\_CFG according to the desired averaging factor (refer to datasheet for DEC2\_CFG values)

#### Step 4: Enable Motion Interrupt

• In INT\_ENABLE register (0x38) set WOM\_INT\_EN[2:0] = b111 to enable motion interrupt

Once triggered, WOM interrupt is generated on INT pin (if INT2\_EN bit is set to 0 for IAM-20680HT) or on INT2 pin (if INT2\_EN is set to 1 for IAM-20680HT)

#### Step 5: Set Motion Threshold

In ACCEL\_WOM\_THR register (0x1F) set the desired motion threshold (1lsb = 4mg, regardless of the selected full-scale)

#### Step 6: Enable Accelerometer Hardware Intelligence

- In ACCEL\_INTEL\_CTRL register (0x69):

- set ACCEL\_INTEL\_EN = 1 to enable the Wake-on-Motion detection logic

- choose ACCEL\_INTEL\_MODE = 0 or 1 to select the detection mode. (see sections 4.1.1, 4.1.2)

- ensure bit 0 is set to 0.

#### Step 7: Set Accelerometer WoM ODR Selection

In LP\_MODE\_CFG register (0x1E) set ACCEL\_WOM\_ODR\_CTRL[3:0] (refer to datasheet for ACCEL\_WOM\_ODR\_CTRL values)

#### Step 8: Enable Accelerometers and WoM Mode

- In PWR\_MGMT\_2 register (0x6C) set STBY\_XA = STBY\_YA = STBY\_ZA = 0, and STBY\_XG = STBY\_YG = STBY\_ZG = 1

- In PWR\_MGMT\_1 register (0x6B) set ACCEL\_CYCLE = 1

### **4** WAKE-ON-MOTION CONFIGURATIONS

Some of key behavior for Wake-on-Motion are described in this section for better understanding.

#### 4.1. WOM TRIGGERING MODE SETTING BY ACCEL\_INTEL\_MODE

Wake-On-Motion interrupt is generated when, on any of the three axes, the difference between acceleration measured by the axis and a reference value exceeds the threshold specified in the configuration phase. User can select between two detection modes, based on the reference value considered:

- Mode 0: Absolute acceleration (measured acceleration value is compared to the value sampled at the activation of WOM functionality)

- Mode 1: Relative acceleration (measured acceleration value is compared to the immediately previous value sampled)

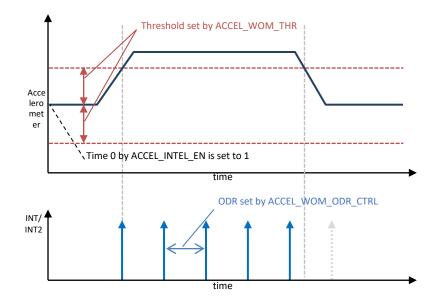

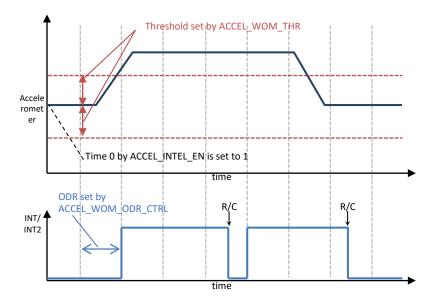

#### 4.1.1. ACCEL\_INTEL\_MODE[6] = 0

Compares the current sample to the first sample taken when entering in WoM by ACCEL\_INTEL\_EN = 1.

Figure 2. waveform at ACCEL\_INTEL\_MODE = 0

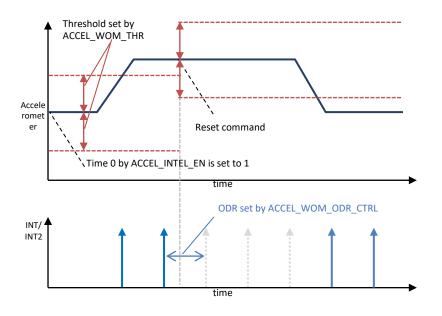

#### 4.1.1.1. reset accelerometer first sample value

To re-initialize the reference accelerometer value to be compared with the current sample, it is required to repeat the enabling sequence described in section 3.

Figure 3. waveform at ACCEL\_INTEL\_MODE = 0

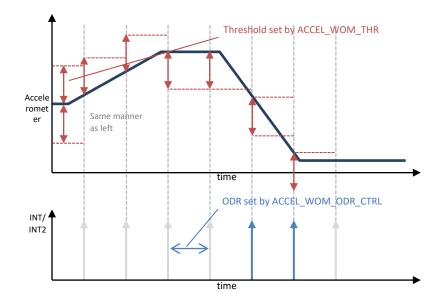

#### 4.1.2. ACCEL\_INTEL\_MODE[6] = 1

Compares the current sample with the previous sample.

Figure 4. waveform at ACCEL\_INTEL\_MODE = 1

#### 4.2. INT PIN STATUS LATCH

By setting LATCH\_INT\_EN = 1, the device's INT pin status can be latched to avoid passing over the signal in case of periodical INT monitoring from HOST. Then, INT pin status can be cleared by register read command, and read clear condition is programmable by INT\_RD\_CLEAR bit in register INT\_PIN\_CFG (0x37).

Key conditions at INT\_PIN\_CFG(0x37) in example below: Bit 7 (INT\_LEVEL) = 0 (The logic level for INT/INT2 pin is active high.) Bit 6 (INT\_OPEN) = 0 (INT/INT2 pin is configured as push-pull.) Bit 5 (LATCH\_INT\_EN) = 1 (INT/INT2 pin level held until interrupt status is cleared.)

Figure 5. waveform at ACCEL\_INTEL\_MODE = 0

(Note: R/C stands for "read clear")

### 5 STATUS REGISTER UPDATE

The serial interface allows detailed interrupt status information to be read from the Status register any time regardless of the INT pin status. If any interrupt event is happened, the status register is flagged immediately. The interrupt status can be read at address 0x3A (INT\_STATUS). Also, the status register bit information is cleared once the INT status register (INT\_STATUS) is read regardless the INT\_RD\_CLEAR bit condition.

If the INT\_RD\_CLEAR bit is set to b'1, any register read command affects INT\_STATUS register to be cleared. (See details in datasheet about INT\_RD\_CLEAR bit. Below table is a summary of read clear.

| INT_RD_CLEAR bit    | 0          |                 | 1          |                 |

|---------------------|------------|-----------------|------------|-----------------|

| Read at             | INT_STATUS | Other registers | INT_STATUS | Other registers |

| INT pin status      | Cleared    | Keep condition  | Cleared    | Cleared         |

| INT_STATUS register | Cleared    | Keep condition  | Cleared    | Cleared         |

In case of INT\_RD\_CLEAR = 1, if HOST is aware that the INT signal is generated by only WoM event from an INT\_ENABLE register setting standpoint, the HOST can directly read sensor values to clear the INT pin status when the HOST receive the INT signal.

On the other hand, in case of INT\_RD\_CLEAR bit is set to b'0, it is required to read INT\_STATUS register to clear the INT pin status. Otherwise, next INT flagged timing could be not updated due to INT pin flag is maintained.

#### 5.1. WOM FLAG BITS DETAIL

The Wake-on-Motion status register information is updated on bit [7:5] at address 0x3A (INT\_STATUS).

If the WOM\_INT\_EN[2:0] at address 0x38 (INT\_ENABLE) is set to b'111 to enable Wake-on-Motion interrupt on accelerometer and then a Wake-on-Motion event is detected, INT pin asserts high or low depending on address 0x37 (INT\_PIN\_CFG) configuration. Please see datasheet for details. Once Wake-on-Motion event is happened, WOM\_INT[2:0] in address 0x37 (INT\_STATUS) indicates b'010 regardless to which axis detects WoM event. For example, if X & Z axes detect WoM event, then the WOM\_INT[2:0] indicates b'010. See below summary table to help understanding the behavior.

Also, the status register can be flagged even if the WOM\_INT\_EN[2:0] bit is NOT enabled (= b'000). That means the device is capable to detect and report WoM events without INT pin signal flag.

|                 | Flag bit   |            |            |  |

|-----------------|------------|------------|------------|--|

| Motion on axis: | WOM_INT[2] | WOM_INT[1] | WOM_INT[0] |  |

| Х               | 0          | 1          | 0          |  |

| Y               | 0          | 1          | 0          |  |

| Z               | 0          | 1          | 0          |  |

| X+Y             | 0          | 1          | 0          |  |

| X+Z             | 0          | 1          | 0          |  |

| Y+Z             | 0          | 1          | 0          |  |

| X+Y+Z           | 0          | 1          | 0          |  |

### 6 REVISION HISTORY

| REVISION DATE | REVISION | DESCRIPTION     |

|---------------|----------|-----------------|

| 11/27/2023    | 1.0      | Initial release |

This information furnished by InvenSense or its affiliates ("TDK InvenSense") is believed to be accurate and reliable. However, no responsibility is assumed by TDK InvenSense for its use, or for any infringements of patents or other rights of third parties that may result from its use. Specifications are subject to change without notice. TDK InvenSense reserves the right to make changes to this product, including its circuits and software, in order to improve its design and/or performance, without prior notice. TDK InvenSense makes no warranties, neither expressed nor implied, regarding the information and specifications contained in this document. TDK InvenSense assumes no responsibility for any claims or damages arising from information contained in this document, or from the use of products and services detailed therein. This includes, but is not limited to, claims or damages based on the infringement of patents, copyrights, mask work and/or other intellectual property rights.

Certain intellectual property owned by InvenSense and described in this document is patent protected. No license is granted by implication or otherwise under any patent or patent rights of InvenSense. This publication supersedes and replaces all information previously supplied. Trademarks that are registered trademarks are the property of their respective companies. TDK InvenSense sensors should not be used or sold in the development, storage, production or utilization of any conventional or mass-destructive weapons or for any other weapons or life-threatening applications, as well as in any other life critical applications such as medical equipment, transportation, aerospace and nuclear instruments, undersea equipment, power plant equipment, disaster prevention and crime prevention equipment.

©2023 InvenSense. All rights reserved. InvenSense, MotionTracking, MotionProcessing, MotionProcessor, MotionFusion, MotionApps, DMP, AAR, and the InvenSense logo are trademarks of InvenSense, Inc. The TDK logo is a trademark of TDK Corporation. Other company and product names may be trademarks of the respective companies with which they are associated.

©2023 InvenSense. All rights reserved.